CMOS工藝是在PMOS和NMOS工藝基礎上發展起來的。CMOS中的C表示“互補”,即將NMOS器件和PMOS器件同時制作在同一硅襯底上,制作CMOS集成電路。CMOS集成電路具有功耗低、速度快、抗干擾能力強、集成度高等眾多優點。

CMOS電路中既包含NMOS晶體管也包含PMOS晶體管,NMOS晶體管是做在P型硅襯底上的,而PMOS晶體管是做在N型硅襯底上的,要將兩種晶體管都做在同一個硅襯底上,就需要在硅襯底上制作一塊反型區域,該區域被稱為“阱”。根據阱的不同,CMOS工藝分為P阱CMOS工藝、N阱CMOS工藝以及雙阱CMOS工藝。其中N阱CMOS工藝由于工藝簡單、電路性能較P阱CMOS工藝更優,從而獲得廣泛的應用。

cmos工藝流程

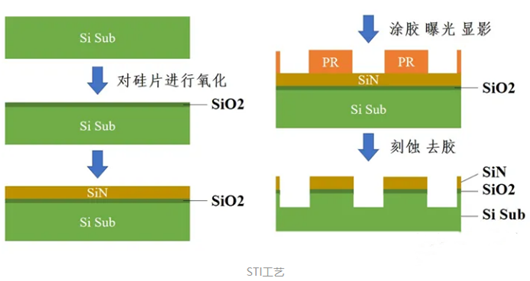

a、隔離氧化層(清洗硅片,對硅片表面進行氧化形成墊氧化層)

注:幾nm厚度,作為隔離層保護有源區在去掉氮化物過程中免受化學污染,同時起到緩和硅襯底與SiN層之間應力的作用。

b、沉積SiN(數百nm厚度,采用LPCVD,即低壓化學氣相沉積法沉積,使用NH3與SiCl2反應,生成SiN)

注:SiN是一種堅固的掩膜材料,用于進行STI工藝時保護有源區,同時其可充當CMP的拋光阻擋材料。

c、涂膠,曝光,顯影,刻蝕掉沒有光刻膠保護的區域,從而在STI區域形成淺溝槽

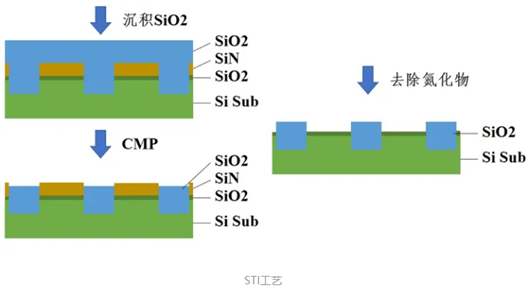

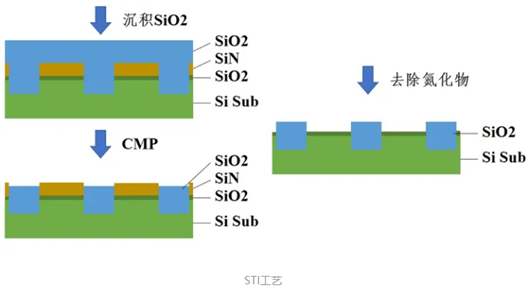

d、用CVD法沉積SiO2膜(SiO2用來阻止氧分子往有源區擴散)

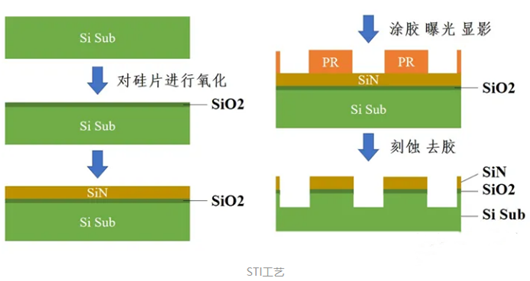

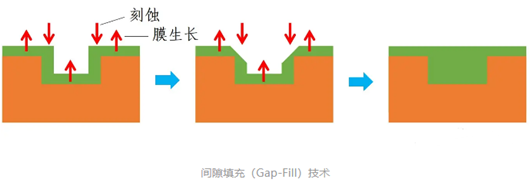

使用間隙填充(Gap-Fill)技術來沉積STI的氧化層,需同時進行成膜與刻蝕工藝。

在膜生長同時進行濺射刻蝕→轉角處的刻蝕速率比平坦部分高,轉角處被刻蝕掉→可以避免在間隙入口處產生夾斷,導致間隙填充中的孔洞→完成薄膜沉積

e、使用CMP對SiO2進行拋光(堅固的SiN充當拋光阻擋層,阻止隔離結構的過度拋光)

f、去除氮化物(熱磷酸槽去除氮化物)

阱(Well)

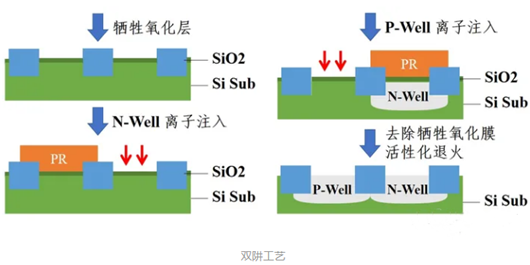

① 雙阱

n型雜質的深擴散區(多數載流子為電子);p型雜質的深擴散區(多數載流子為空穴)

② 工藝流程

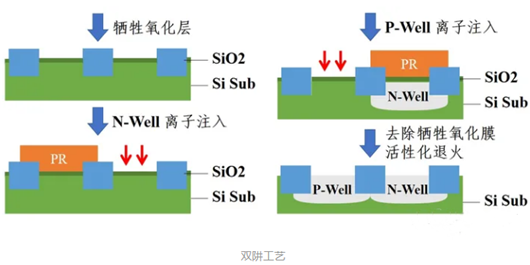

a、在硅晶圓上用熱氧化工藝形成犧牲氧化層(作用是在離子注入形成阱時調整離子注入深度)

b、在P/N阱區域上方涂光刻膠并用光刻工藝進行曝光,顯影,并用離子注入工藝注入n/p雜質,灰化去除不需要的光刻膠

c、除去犧牲氧化膜,將n型和p型阱區退火激活,形成雙阱

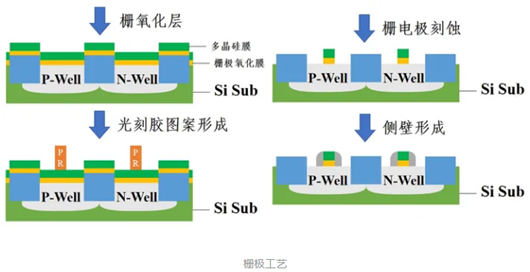

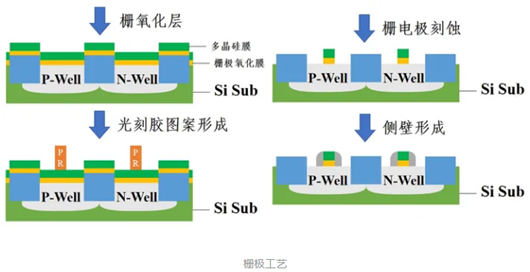

柵極

① 柵極:先進的數字電路需要高速和低壓工作,需實現柵極長度的小型化(通過微細化工藝減小柵極長度)

② 自對準工藝:柵極形成是在源漏極形成之前完成,利用自對準工藝形成源漏極,可省略一道光刻工序,從而降低成本

③ 工藝流程

a、在雙阱上形成柵氧化層,作為柵極材料的多晶硅層、金屬硅化物的多層膜(減壓CVD法)

b、用光刻工藝對柵電極進行阻擋涂改

c、對多晶硅膜進行干法刻蝕,用去膠工藝去除不需要的光刻膠

d、用等離子CVD法形成SiO2層,自對準的在柵電極兩側形成LDD膜

[緩和晶體管中微細尺寸的柵電極附近的電場]

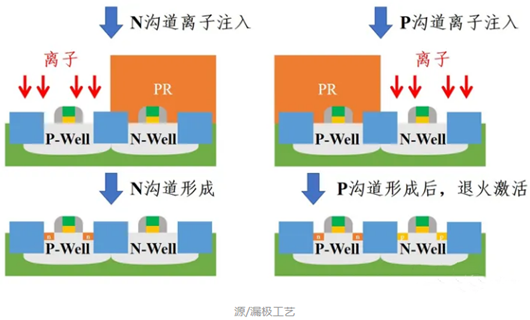

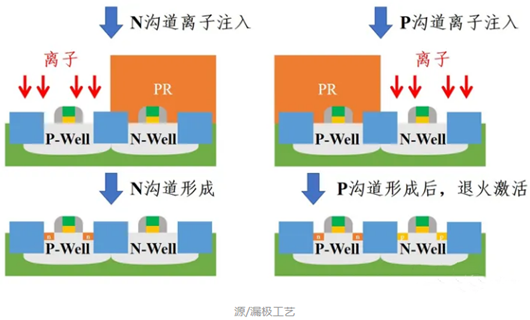

源極/漏極

① 源極與漏極

MOS管通過施加到柵極的電壓執行開關操作,以打開和關閉源極與漏極之間的電流。

② 工藝流程

a、通過光刻工藝在n阱區域上覆蓋光刻膠,并將n型雜質離子注入p型區域

b、使用高電流型的離子注入設備向源漏極注入高濃度的雜質

c、灰化去除不需的光刻膠

d、n阱區域同理

e、退火激活形成n型和p型晶體管的源漏極區域

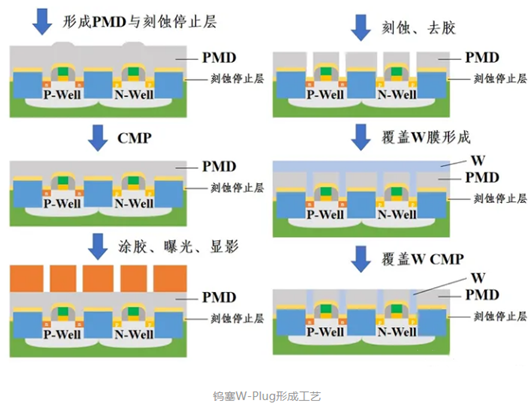

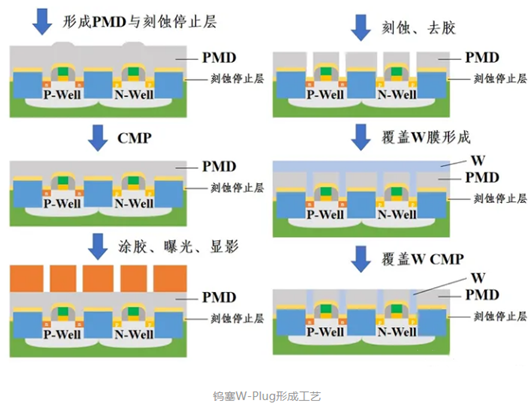

電極形成(鎢塞W-Plug形成)

工藝流程

a、用等離子CVD法形成刻蝕停止層和隔離層(隔離層是金屬布線層形成之前的絕緣層,稱為PMD[Pre Metal Dielectrics])

b、用CMP工藝使得隔離層平坦化(受柵電極的影響,上部的形狀會產生凸起)

c、用光刻法形成接觸孔的圖形(微細尺寸的源漏極和接觸必須連接上,且要采取最小的布線間距)

d、用光刻膠作為掩膜來刻蝕隔離層,穿透形成接觸孔

e、灰化去除不需要的光刻膠

f、在接觸孔內形成TiN/Ti等黏附層和覆蓋W層

注:黏附層將隔離層和W膜更好地黏接到一起,用濺射工藝生成;覆蓋式W膜用CVD法形成

g、用CMP工藝去除PMD上多余的W層和黏附層,實現W塞

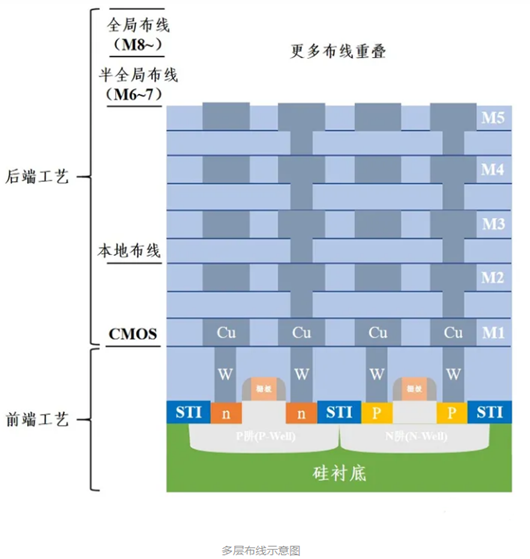

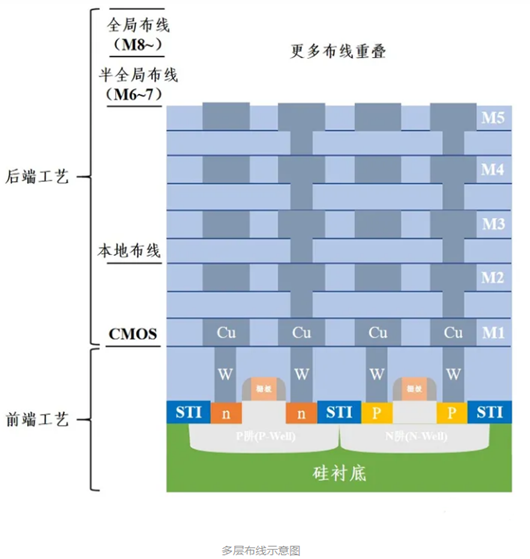

后端工藝

1、Why使用多層布線

在先進的邏輯IC中,把已經驗證完成的IP進行整合,進而完成數字IC的設計。新的電路的驗證需要花費大量的時間,通常是把各種各樣的電路模塊通過布線連接到一起來實現該LSI。

2、多層布線示意圖

〈烜芯微/XXW〉專業制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以直接聯系下方的聯系號碼或加QQ/微信,由我們的銷售經理給您精準的報價以及產品介紹

〈烜芯微/XXW〉專業制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以直接聯系下方的聯系號碼或加QQ/微信,由我們的銷售經理給您精準的報價以及產品介紹

聯系號碼:18923864027(同微信)

QQ:709211280